# Electronics II – Chapter 4 Boolean Algebra and Logic Simplification

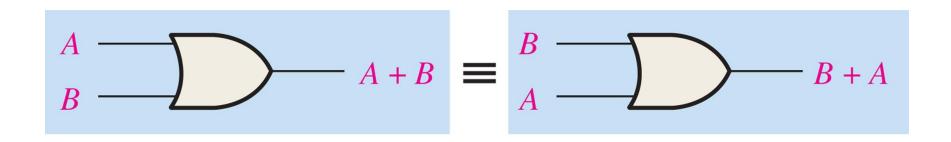

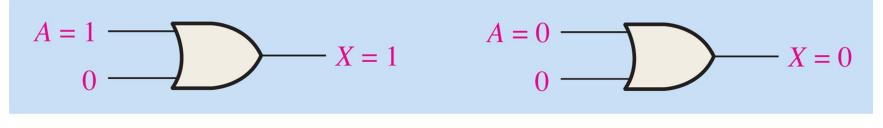

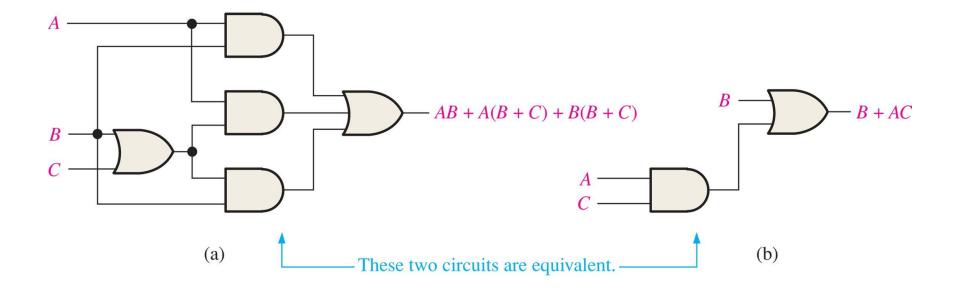

**FIGURE 4-3** Application of commutative law of addition.

Electronics II

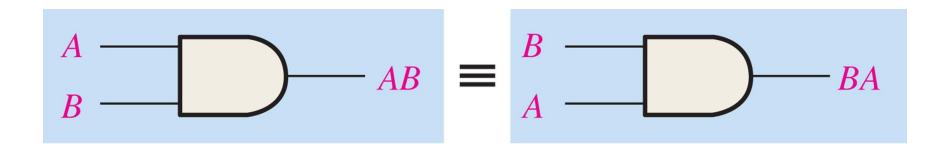

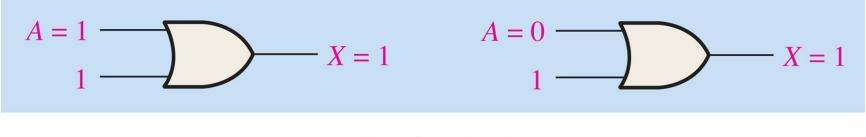

**FIGURE 4-4** Application of commutative law of multiplication.

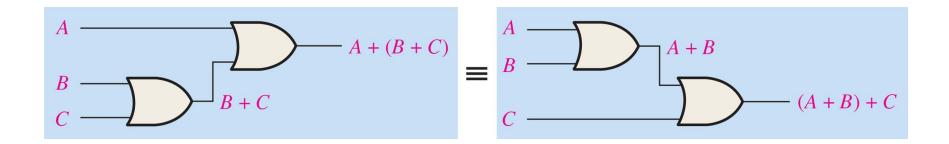

**FIGURE 4-5** Application of associative law of addition.

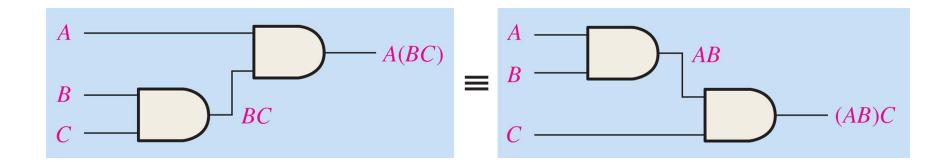

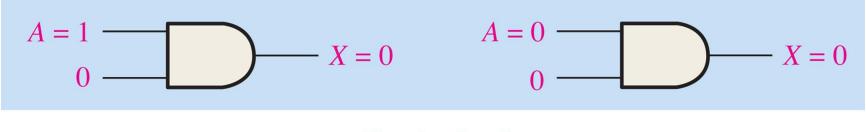

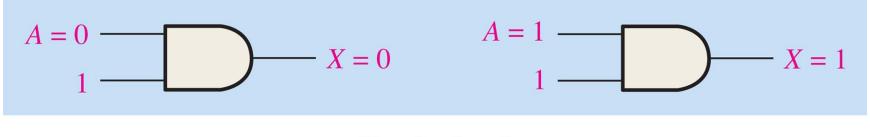

**FIGURE 4-6** Application of associative law of multiplication.

# TABLE 4–1

Basic rules of Boolean algebra.

| <b>1.</b> $A + 0 = A$            | 7. $A \cdot A = A$                     |

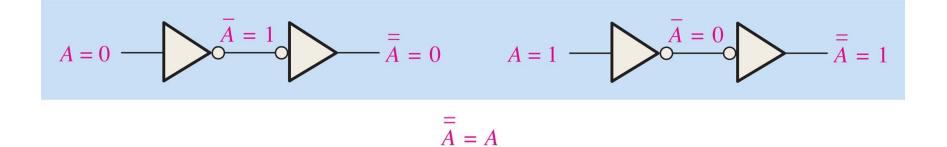

|----------------------------------|----------------------------------------|

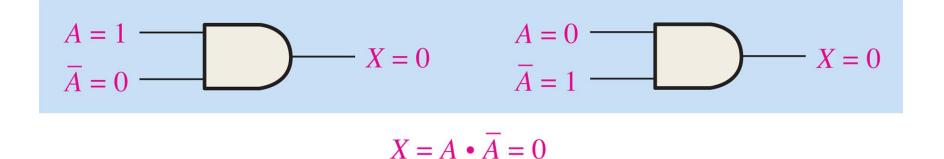

| <b>2.</b> $A + 1 = 1$            | 8. $A \cdot \overline{A} = 0$          |

| <b>3.</b> $A \cdot 0 = 0$        | 9. $\overline{\overline{A}} = A$       |

| <b>4.</b> $A \cdot 1 = A$        | <b>10.</b> $A + AB = A$                |

| <b>5.</b> $A + A = A$            | <b>11.</b> $A + \overline{A}B = A + B$ |

| <b>6.</b> $A + \overline{A} = 1$ | <b>12.</b> $(A + B)(A + C) = A + BC$   |

A, B, or C can represent a single variable or a combination of variables.

X = A + 0 = A

Electronics II

X = A + 1 = 1

$X = A \bullet 0 = 0$

$X = A \bullet 1 = A$

X = A + A = A

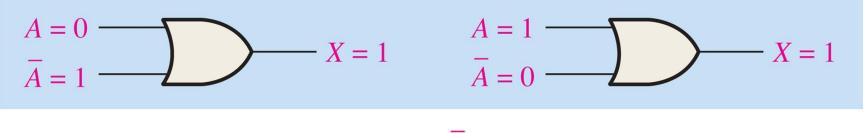

$X = A + \overline{A} = 1$

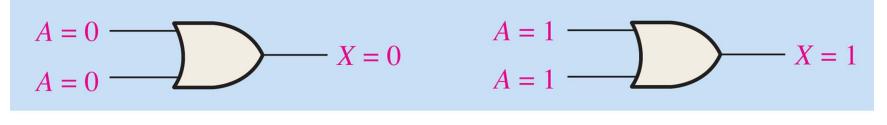

$$A = 0$$

$$A = 0$$

$$X = 0$$

$$A = 1$$

$$X = 1$$

$$A = 1$$

$X = A \bullet A = A$

## **TABLE 4–2**

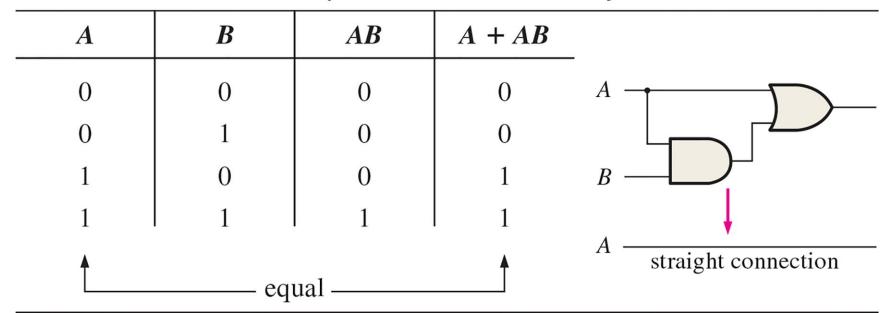

Rule 10: A + AB = A. Open file T04-02 to verify.

## TABLE 4-3

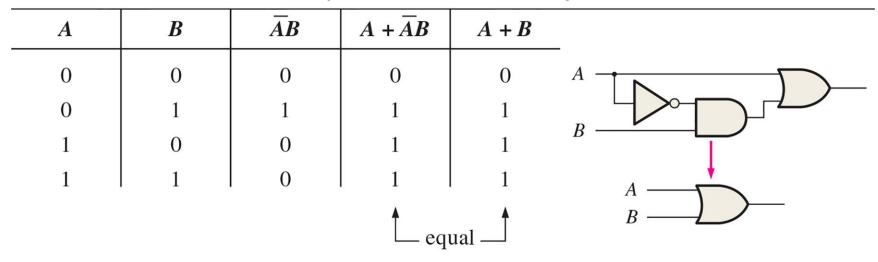

Rule 11:  $A + \overline{A}B = A + B$ . Open file T04-03 to verify.

### TABLE 4-4

| Rule 12: $(A + B)(A + C) = A + BC$ . Open file 7 | T04-04 to verify. |

|--------------------------------------------------|-------------------|

|--------------------------------------------------|-------------------|

| A | В | С | A + B | A + C | (A+B)(A+C) | BC         | A + BC   |                   |

|---|---|---|-------|-------|------------|------------|----------|-------------------|

| 0 | 0 | 0 | 0     | 0     | 0          | 0          | 0        |                   |

| 0 | 0 | 1 | 0     | 1     | 0          | 0          | 0        |                   |

| 0 | 1 | 0 | 1     | 0     | 0          | 0          | 0        |                   |

| 0 | 1 | 1 | 1     | 1     | 1          | 1          | 1        | $c \rightarrow c$ |

| 1 | 0 | 0 | 1     | 1     | 1          | 0          | 1        |                   |

| 1 | 0 | 1 | 1     | 1     | 1          | 0          | 1        | •                 |

| 1 | 1 | 0 | 1     | 1     | 1          | 0          | 1        |                   |

| 1 | 1 | 1 | 1     | 1     | 1          | 1          | 1        | $\tilde{c}$       |

|   |   |   |       |       | t          | — equal —— | <b>↑</b> |                   |

**FIGURE 4-17** Gate equivalencies and the corresponding truth tables that illustrate DeMorgan's theorems. Notice the equality of the two output columns in each table. This shows that the equivalent gates perform the same logic function.

|                                          |                                                 | Inputs | Outp                           | out                           |

|------------------------------------------|-------------------------------------------------|--------|--------------------------------|-------------------------------|

|                                          |                                                 | X Y    | $\overline{XY}$ $\overline{X}$ | $\overline{X} + \overline{Y}$ |

| $X \longrightarrow \overline{XY} \equiv$ | $X \longrightarrow \overline{X} + \overline{Y}$ | 0 0    | 1                              | 1                             |

|                                          |                                                 | 0 1    | 1                              | 1                             |

| NAND                                     | Negative-OR                                     | 1 0    | 1                              | 1                             |

|                                          |                                                 | 1 1    | 0                              | 0                             |

|                                          |                                                 |        |                                |                               |

|                                          |                                                 | Inputs | Outp                           | out                           |

|                                          |                                                 | X Y    | $\overline{X+Y}$               | $\overline{X}\overline{Y}$    |

| X $X + Y$                                | $\equiv \frac{X}{Y} - \frac{x}{\sqrt{y}}$       | 0 0    | 1                              | 1                             |

|                                          |                                                 | 0 1    | 0                              | 0                             |

| NOR                                      | Negative-AND                                    | 1 0    | 0                              | 0                             |

|                                          |                                                 | 1 1    | 0                              | 0                             |

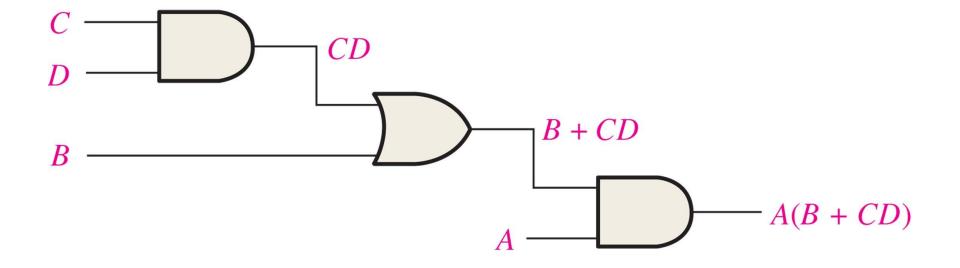

**FIGURE 4-18** A combinational logic circuit showing the development of the Boolean expression for the output.

### TABLE 4–5

## Truth table for the logic circuit in Figure 4–18.

|                  | Inp | outs |   | Output    |

|------------------|-----|------|---|-----------|

| $\boldsymbol{A}$ | В   | С    | D | A(B + CD) |

| 0                | 0   | 0    | 0 | 0         |

| 0                | 0   | 0    | 1 | 0         |

| 0                | 0   | 1    | 0 | 0         |

| 0                | 0   | 1    | 1 | 0         |

| 0                | 1   | 0    | 0 | 0         |

| 0                | 1   | 0    | 1 | 0         |

| 0                | 1   | 1    | 0 | 0         |

| 0                | 1   | 1    | 1 | 0         |

| 1                | 0   | 0    | 0 | 0         |

| 1                | 0   | 0    | 1 | 0         |

| 1                | 0   | 1    | 0 | 0         |

| 1                | 0   | 1    | 1 | 1         |

| 1                | 1   | 0    | 0 | 1         |

| 1                | 1   | 0    | 1 | 1         |

| 1                | 1   | 1    | 0 | 1         |

| 1                | 1   | 1    | 1 | 1         |

Electronics II

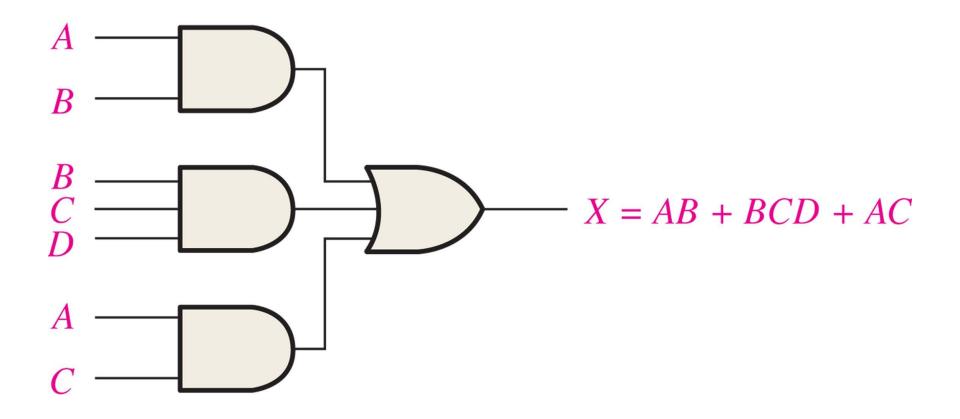

**FIGURE 4-22** Implementation of the SOP (Sum-Of-Products) expression *AB* + *BCD* + *AC*.

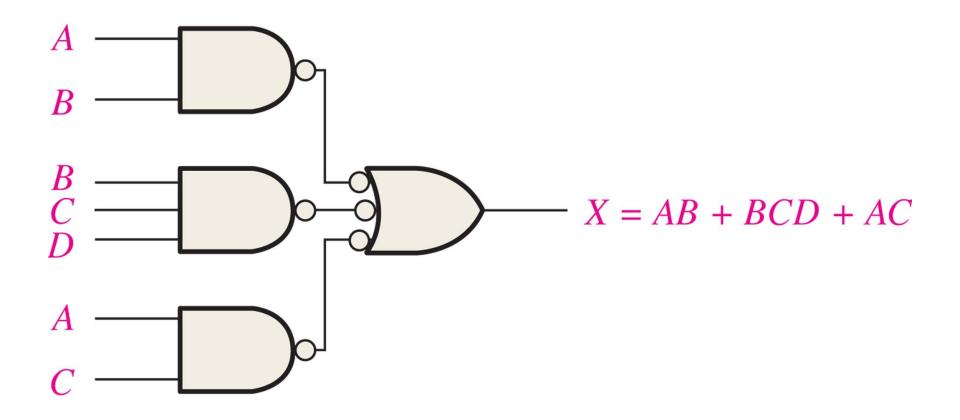

**FIGURE 4-23** This NAND/NAND implementation is equivalent to the AND/OR in Figure 4–22.

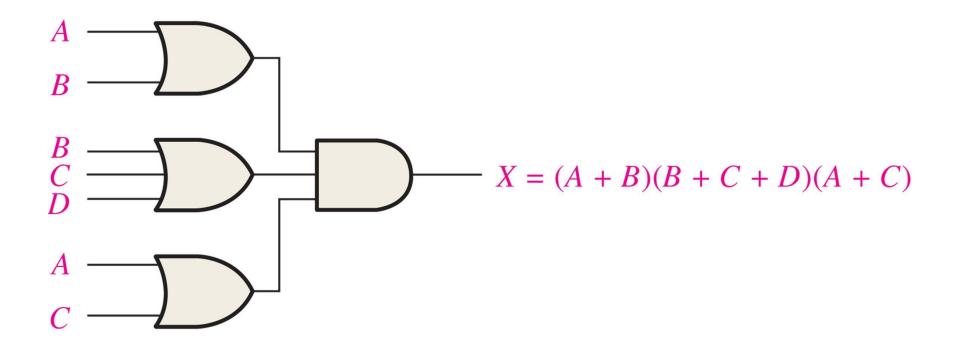

**FIGURE 4-24** Implementation of the POS (Sum-Of-Products) expression (A + B)(B + C + D)(A + C).

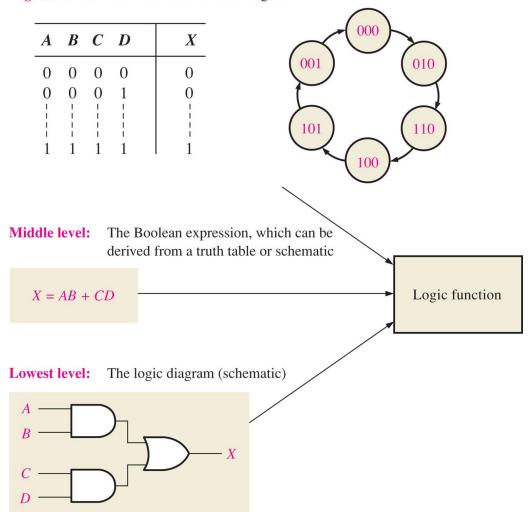

#### **FIGURE 4-49** Illustration of the three levels of abstraction for describing a logic function.

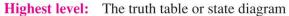

#### FIGURE 4-50 Seven-segment display.

0 | 2 3 4 5 6 7 8 9 8 6 C 3 E F 6 H | 1 L P U

(a) Segment arrangement

(b) Formation of the ten digits and certain letters

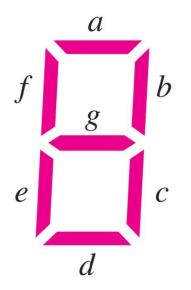

# **TABLE 4–14**

Active segments for each of the five letters used in the system display.

| Segments Activated                                   |  |  |

|------------------------------------------------------|--|--|

| a, b, c, e, f, g                                     |  |  |

| <i>c</i> , <i>d</i> , <i>e</i> , <i>f</i> , <i>g</i> |  |  |

| a, d, e, f                                           |  |  |

| b, c, d, e, g                                        |  |  |

| a, d, e, f, g                                        |  |  |

|                                                      |  |  |

(a)

(b)

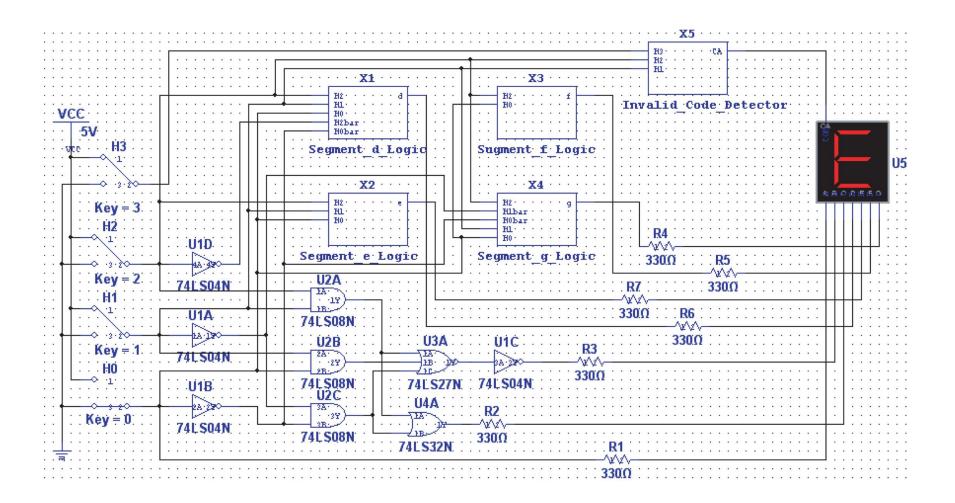

FIGURE 4-54 Multisim circuit screen for decoder and display.