## Electronics II – Chapter 3 Logic Gates

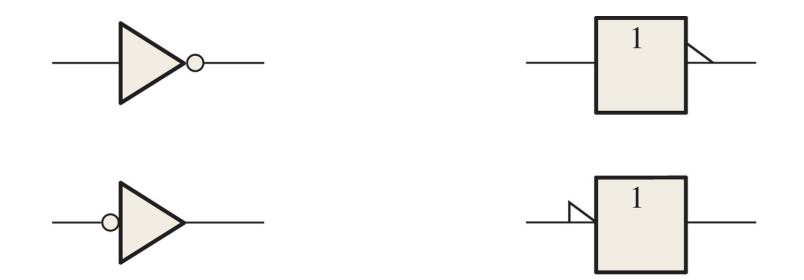

**FIGURE 3-1** Standard logic symbols for the inverter (ANSI/IEEE Std. 91-1984/Std. 91a-1991).

(a) Distinctive shape symbols with negation indicators

(b) Rectangular outline symbols with polarity indicators

# TABLE 3-1

# Inverter truth table.

| Input    | Output   |

|----------|----------|

| LOW (0)  | HIGH (1) |

| HIGH (1) | LOW (0)  |

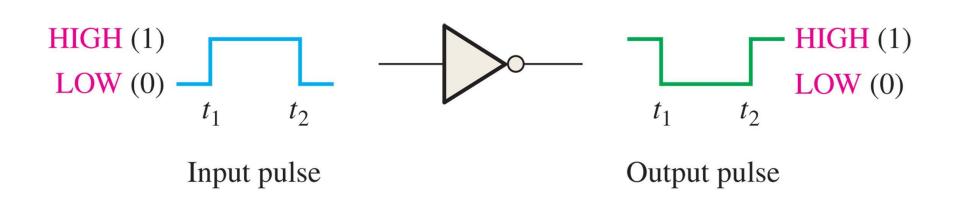

**FIGURE 3-2** Inverter operation with a pulse input.

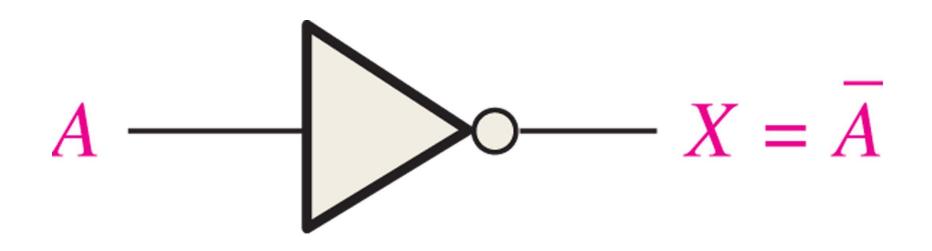

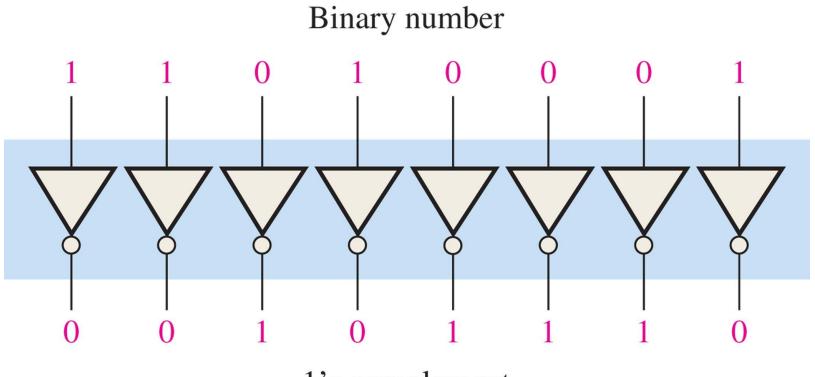

**FIGURE 3-6** The inverter complements an input variable.

**FIGURE 3-7** Example of a 1's complement circuit using inverters.

1's complement

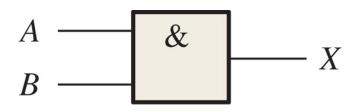

**FIGURE 3-8** Standard logic symbols for the AND gate showing two inputs (ANSI/IEEE Std. 91-1984/Std. 91a-1991).

(a) Distinctive shape

(b) Rectangular outline with the AND (&) qualifying symbol

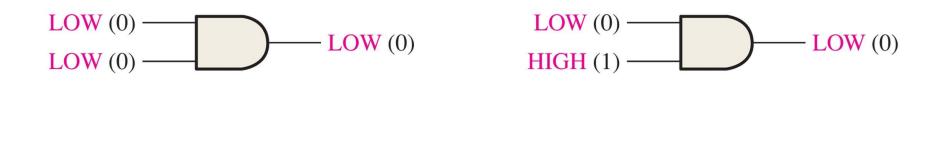

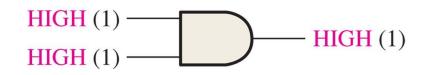

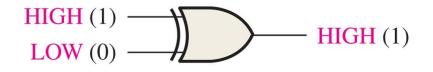

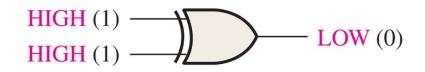

**FIGURE 3-9** All possible logic levels for a 2-input AND gate.

## TABLE 3-2

Truth table for a 2-input AND gate.

| Inp               | outs | Output |

|-------------------|------|--------|

| A                 | B    | X      |

| 0                 | 0    | 0      |

| 0                 | 1    | 0      |

| 1                 | 0    | 0      |

| 1                 | 1    | 1      |

| 1 = HIGH, 0 = LOW |      |        |

## TABLE 3-3

|   | Inputs |   | Output |

|---|--------|---|--------|

| A | B      | С | X      |

| 0 | 0      | 0 | 0      |

| 0 | 0      | 1 | 0      |

| 0 | 1      | 0 | 0      |

| 0 | 1      | 1 | 0      |

| 1 | 0      | 0 | 0      |

| 1 | 0      | 1 | 0      |

| 1 | 1      | 0 | 0      |

| 1 | 1      | 1 | 1      |

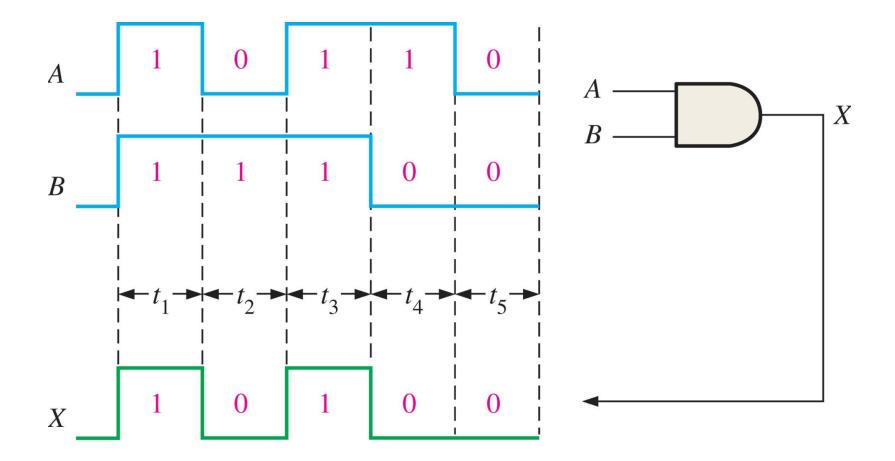

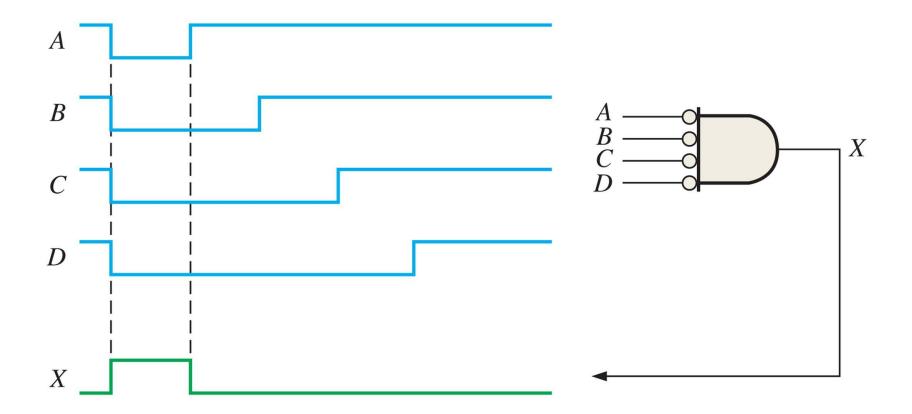

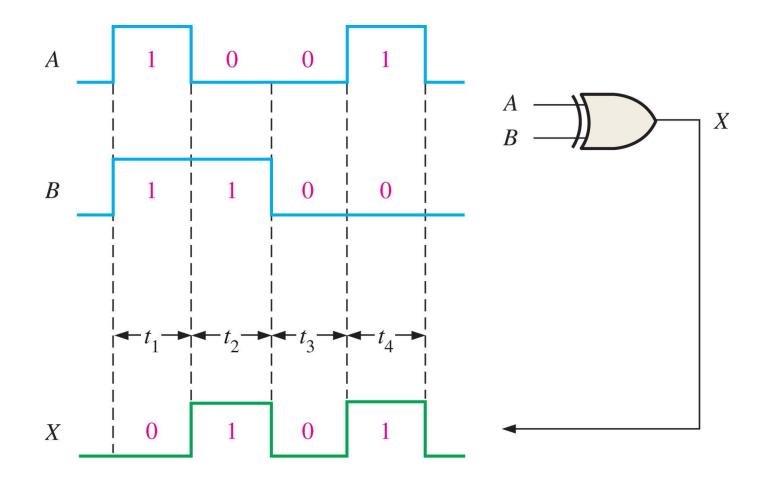

**FIGURE 3-10** Example of AND gate operation with a timing diagram showing input and output relationships.

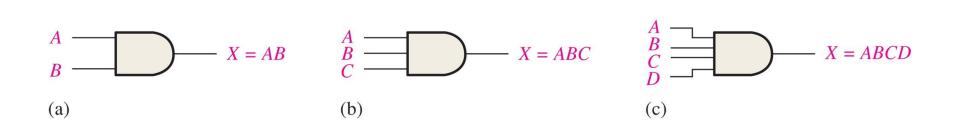

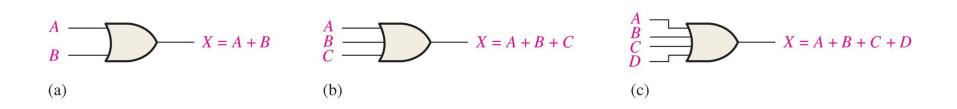

**FIGURE 3-15** Boolean expressions for AND gates with two, three, and four inputs.

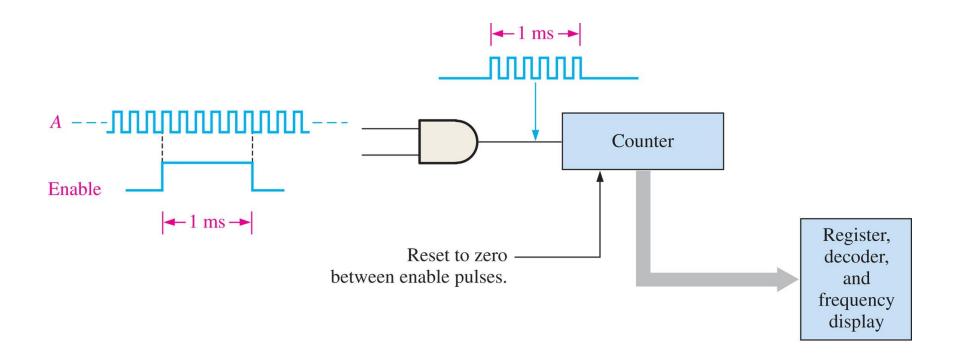

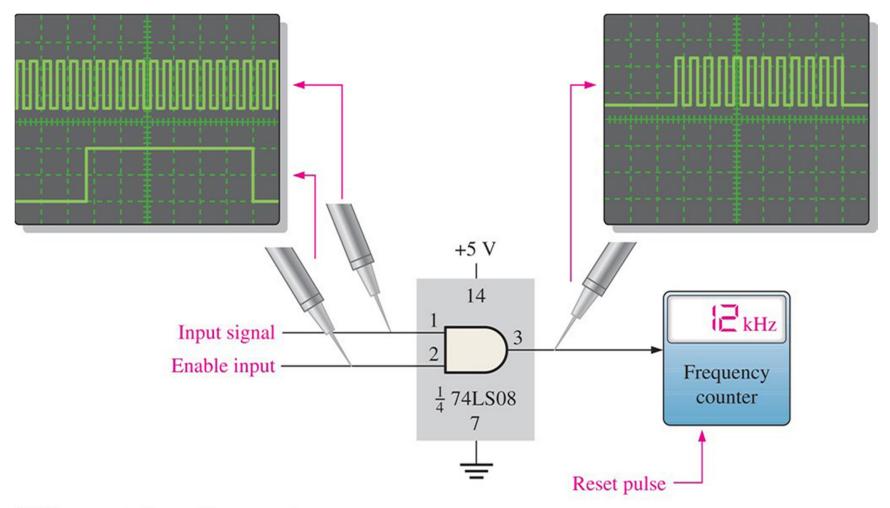

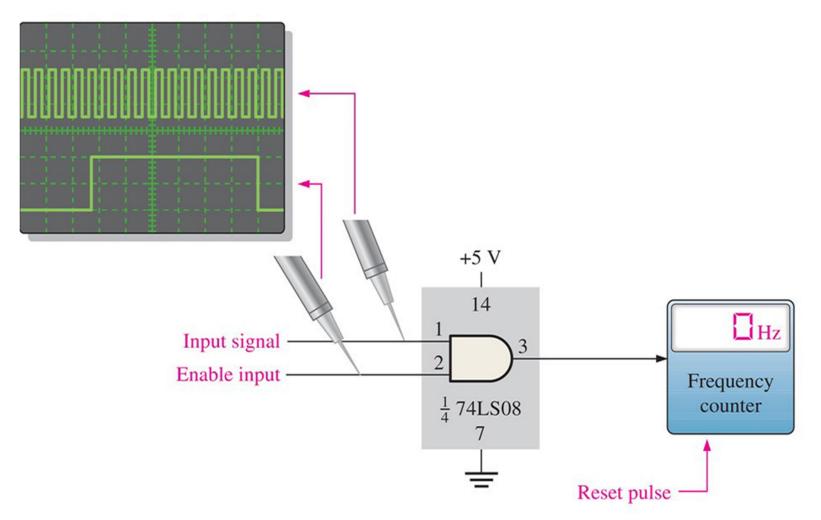

**FIGURE 3-16** An AND gate performing an enable/inhibit function for a frequency counter.

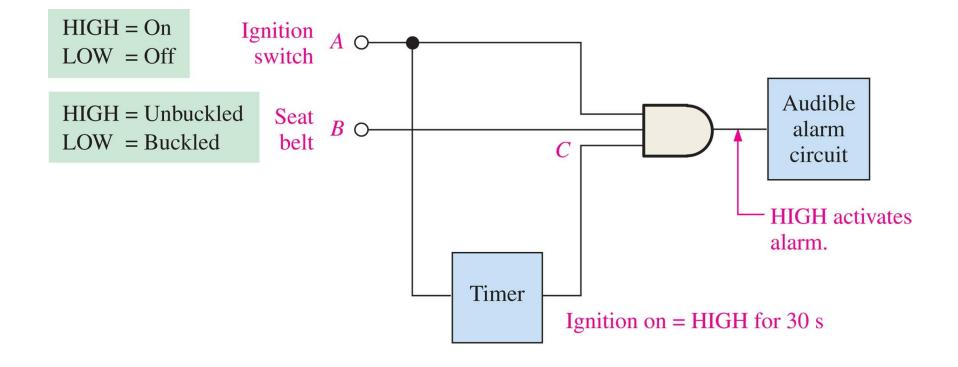

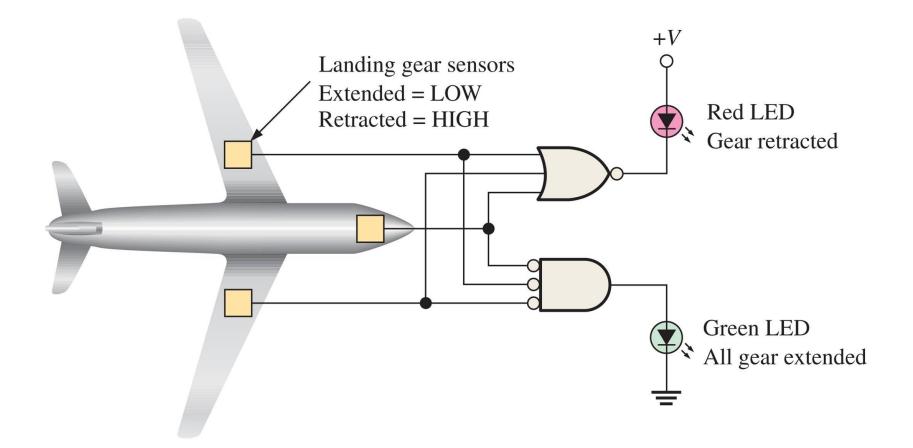

FIGURE 3-17 A simple seat belt alarm circuit using an AND gate.

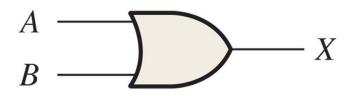

**FIGURE 3-18** Standard logic symbols for the OR gate showing two inputs (ANSI/IEEE Std. 91-1984/Std. 91a-1991).

(a) Distinctive shape

(b) Rectangular outline with the OR (≥ 1) qualifying symbol

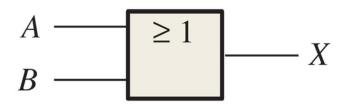

**FIGURE 3-19** All possible logic levels for a 2-input OR gate.

## TABLE 3-5

Truth table for a 2-input OR gate.

| Inputs |   | Output |

|--------|---|--------|

| A      | B | X      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 1      |

|        |   |        |

1 = HIGH, 0 = LOW

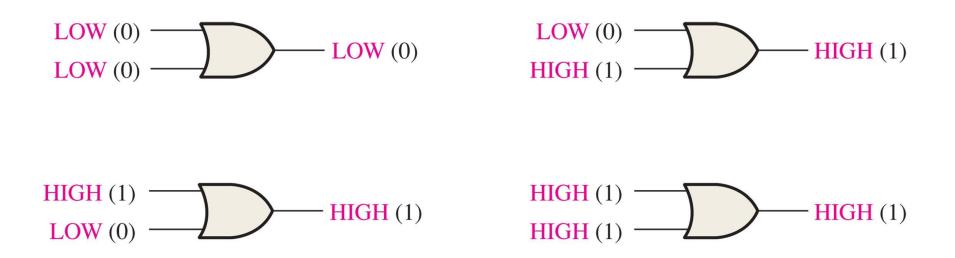

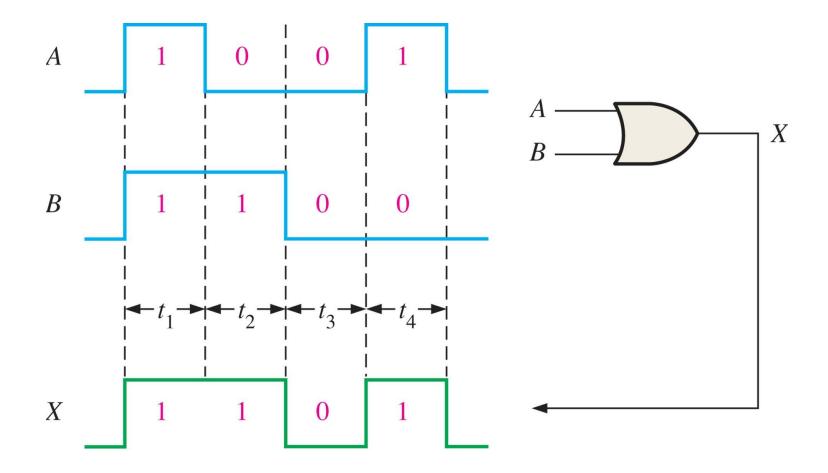

**FIGURE 3-20** Example of OR gate operation with a timing diagram showing input and output time elationships.

**FIGURE 3-24** Boolean expressions for OR gates with two, three, and four inputs.

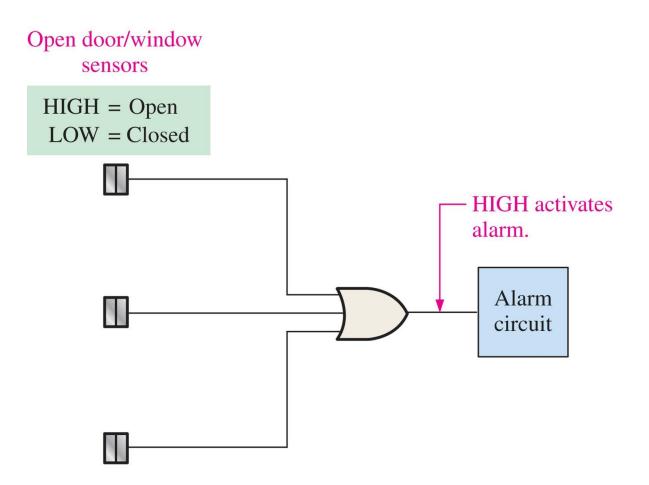

**FIGURE 3-25** A simplified intrusion detection system using an OR gate.

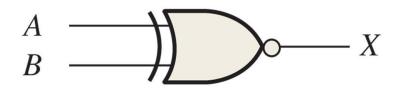

FIGURE 3-26 Standard NAND gate logic symbols (ANSI/IEEE Std. 91-1984/Std. 91a-1991).

(a) Distinctive shape, 2-input NAND gate and its NOT/AND equivalent

(b) Rectangular outline, 2-input NAND gate with polarity indicator

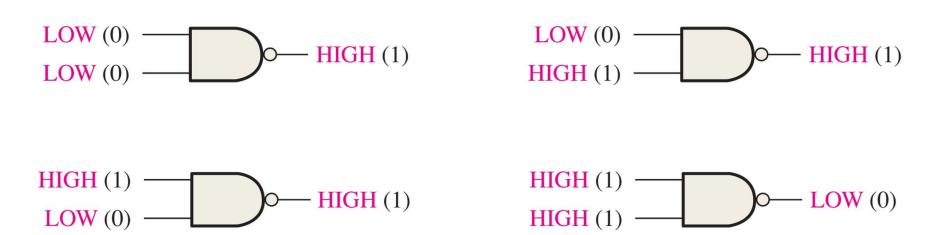

# Truth table for a 2-input NAND gate.

| Inputs |   | Output |

|--------|---|--------|

| A      | B | X      |

| 0      | 0 | 1      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 0      |

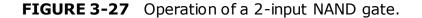

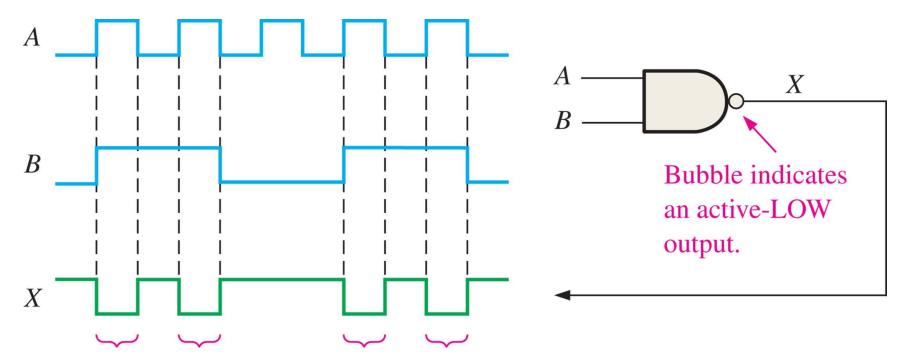

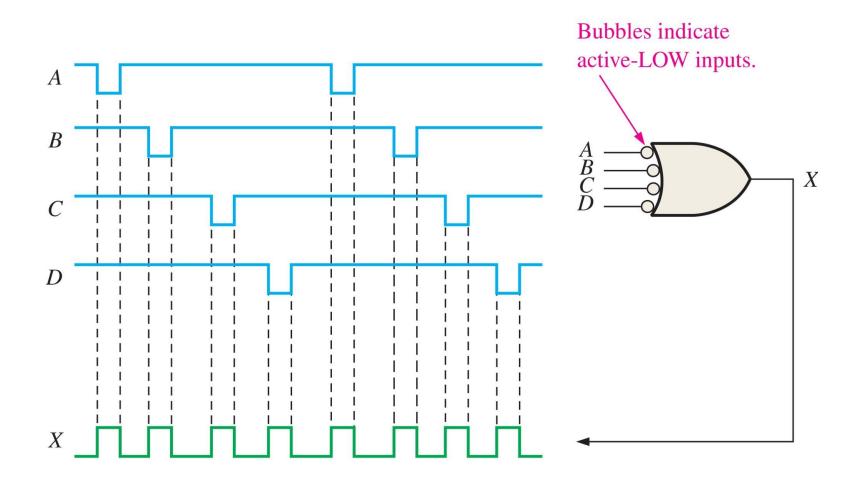

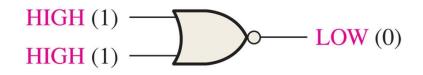

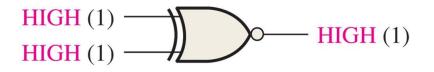

#### **FIGURE 3-28**

A and B are both HIGH during these four time intervals; therefore, X is LOW.

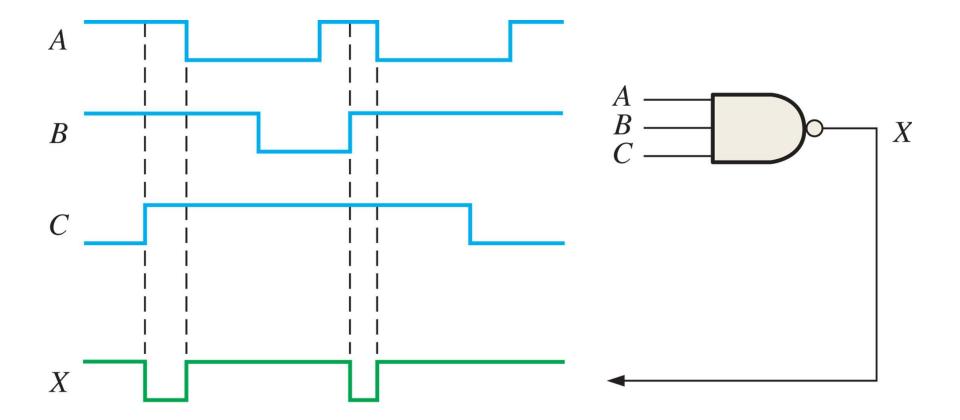

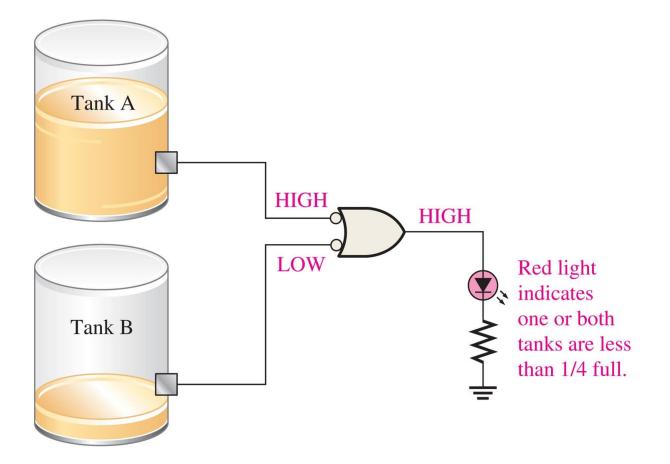

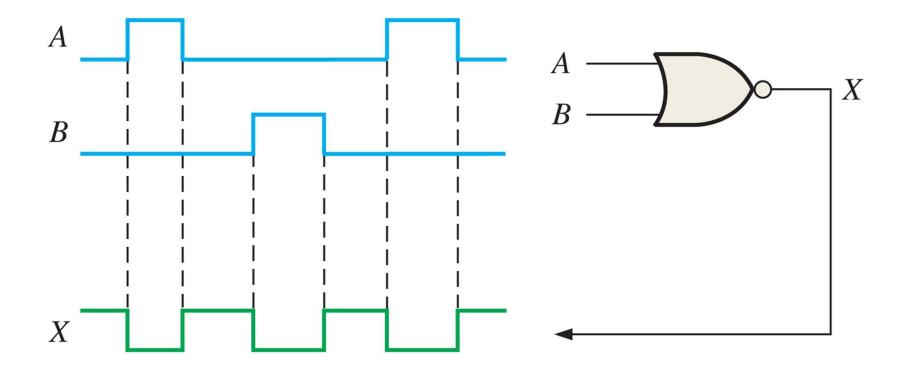

**FIGURE 3-29**

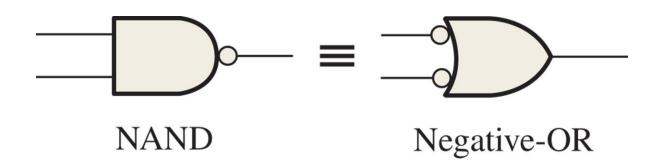

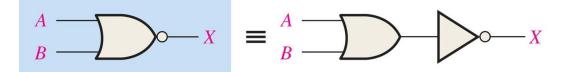

**FIGURE 3-30** ANSI/IEEE standard symbols representing the two equivalent operations of a NAND gate.

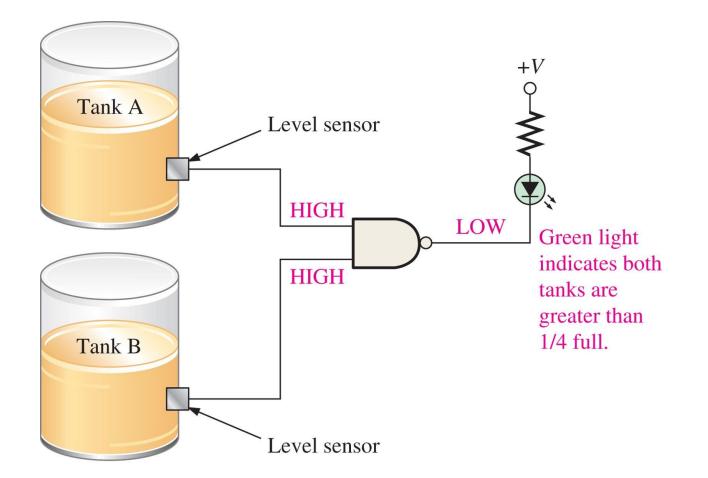

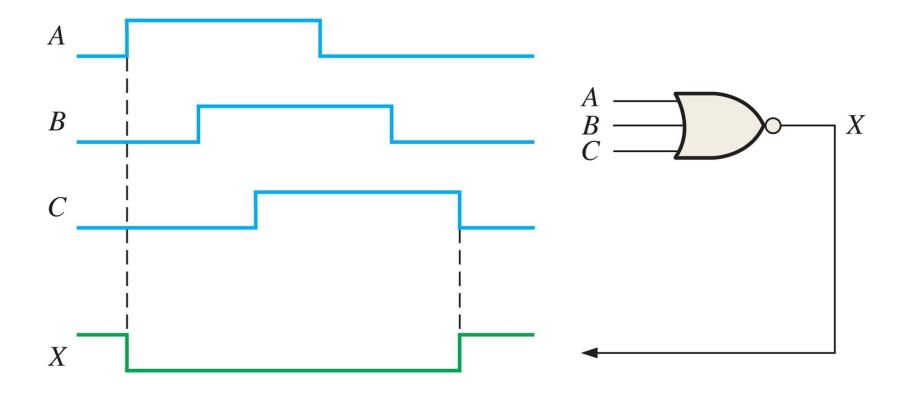

FIGURE 3-31

### **FIGURE 3-32**

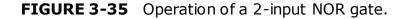

FIGURE 3-34 Standard NOR gate logic symbols (ANSI/IEEE Std. 91-1984/Std. 91a-1991).

(a) Distinctive shape, 2-input NOR gate and its NOT/OR equivalent

(b) Rectangular outline, 2-input NOR gate with polarity indicator

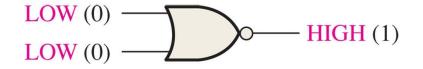

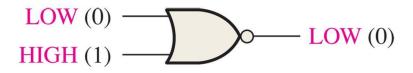

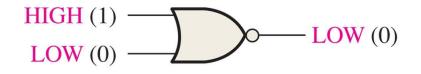

## **TABLE 3–9**

Truth table for a 2-input NOR gate.

| Inp                | outs | Output |

|--------------------|------|--------|

| A                  | B    | X      |

| 0                  | 0    | 1      |

| 0                  | 1    | 0      |

| 1                  | 0    | 0      |

| 1                  | 1    | 0      |

| 1 = HIGH, 0 = LOW. |      |        |

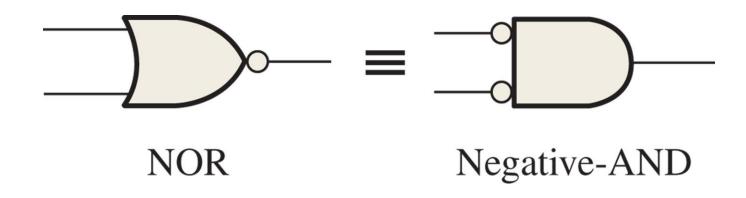

**FIGURE 3-38** Standard symbols representing the two equivalent operations of a NOR gate.

### **FIGURE 3-40**

# FIGURE 3-41

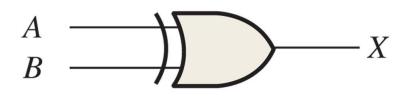

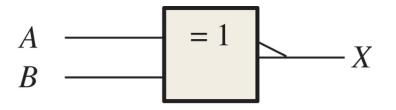

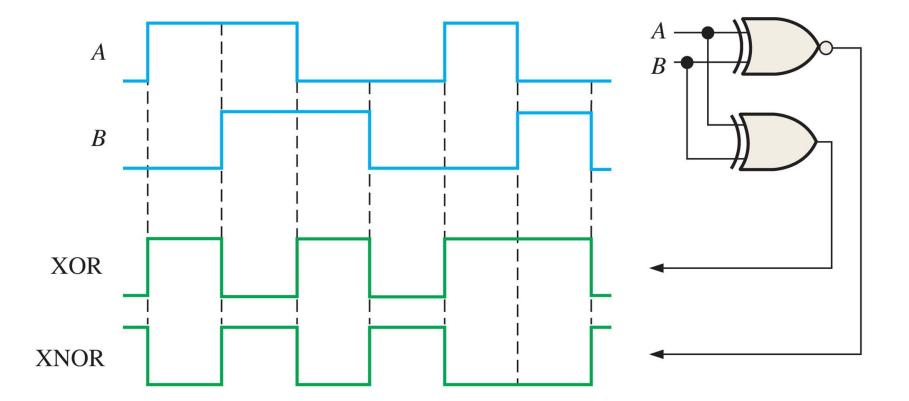

FIGURE 3-42 Standard logic symbols for the exclusive-OR gate.

(a) Distinctive shape

(b) Rectangular outline

Electronics II

# **TABLE 3–11**

# Truth table for an exclusive-OR gate.

| In | puts | Output |

|----|------|--------|

| A  | B    | X      |

| 0  | 0    | 0      |

| 0  | 1    | 1      |

| 1  | 0    | 1      |

| 1  | 1    | 0      |

**FIGURE 3-43** All possible logic levels for an exclusive-OR gate.

Electronics II

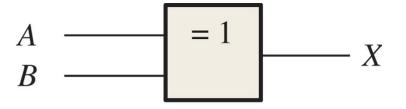

**FIGURE 3-45** Standard logic symbols for the exclusive-NOR gate.

(a) Distinctive shape

(b) Rectangular outline

Electronics II

# **TABLE 3–12**

# Truth table for an exclusive-NOR gate.

|   | Inputs | Output |

|---|--------|--------|

| A | B      | X      |

| 0 | 0      | 1      |

| 0 | 1      | 0      |

| 1 | 0      | 0      |

| 1 | 1      | 1      |

**FIGURE 3-46** All possible logic levels for an exclusive-NOR gate.

$$\frac{\text{LOW}(0)}{\text{LOW}(0)} \longrightarrow \text{HIGH}(1)$$

$$\frac{\text{HIGH}(1)}{\text{LOW}(0)} \longrightarrow \text{LOW}(0)$$

**FIGURE 3-47** Example of exclusive-OR gate operation with pulse waveform inputs.

# **TABLE 3–13**

An XOR gate used to add two bits.

| Inpu | t Bits | <b>Output (Sum)</b> |

|------|--------|---------------------|

| A    | B      | Σ                   |

| 0    | 0      | 0                   |

| 0    | 1      | 1                   |

| 1    | 0      | 1                   |

| 1    | 1      | 0 (without          |

|      | )[     | the 1 carry bit)    |

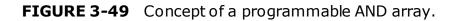

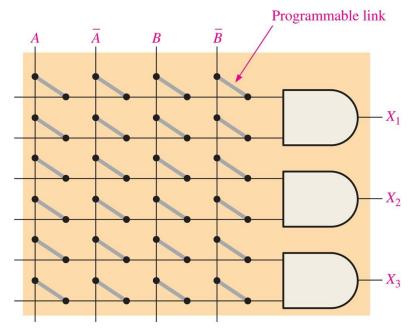

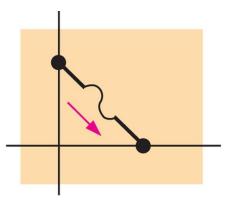

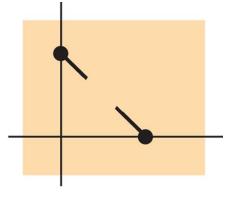

(a) Unprogrammed

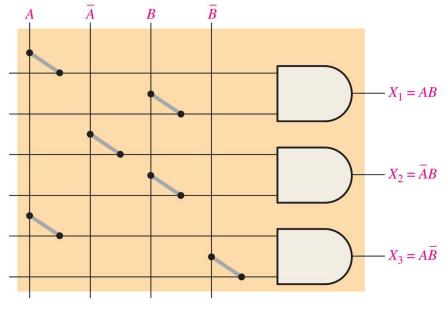

(b) Programmed

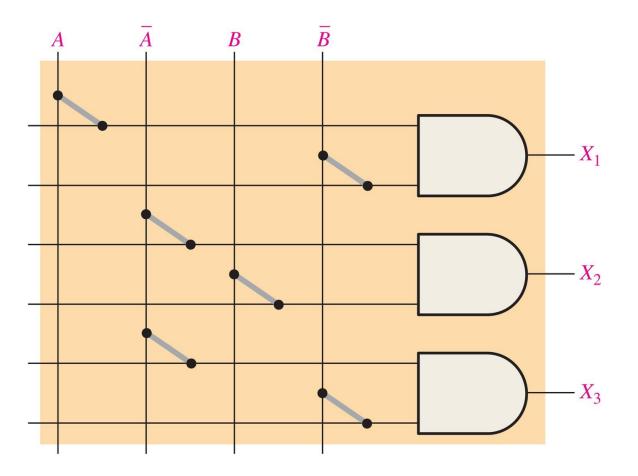

## **FIGURE 3-50**

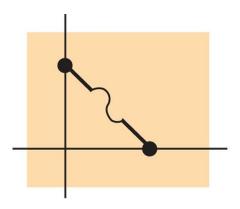

### **FIGURE 3-51** The programmable fuse link.

(a) Fuse intact before programming

(b) Programming current (c) Fuse open after programming

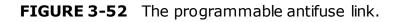

(a) Antifuse is open before programming.

(b) Programming voltage breaks down insulation layer to create contact.

(c) Antifuse is effectively shorted after programming.

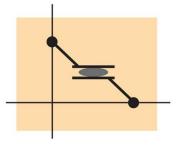

**FIGURE 3-53** A simple AND array with EPROM technology. Only one gate in the array is shown for simplicity.

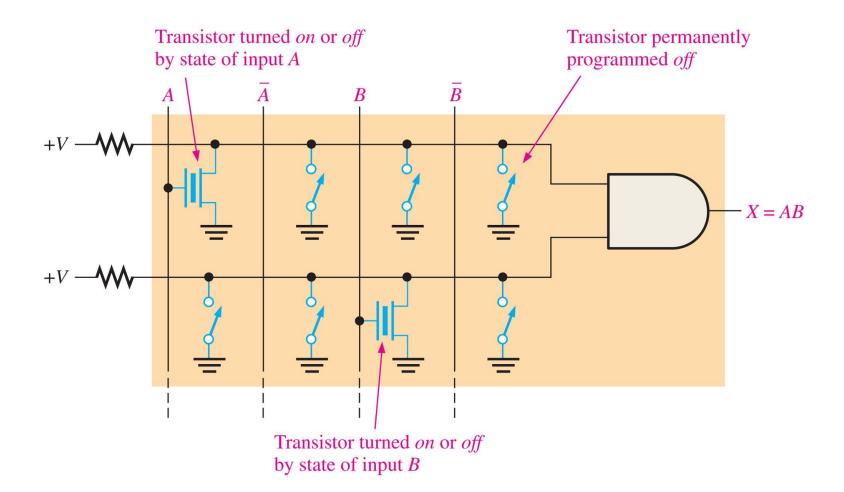

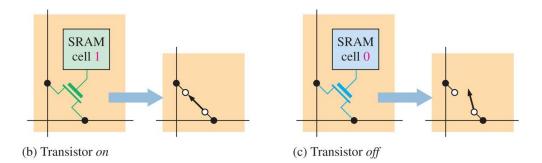

**FIGURE 3-54** Concept of an AND array with SRAM technology.

(a) SRAM-based programmable array

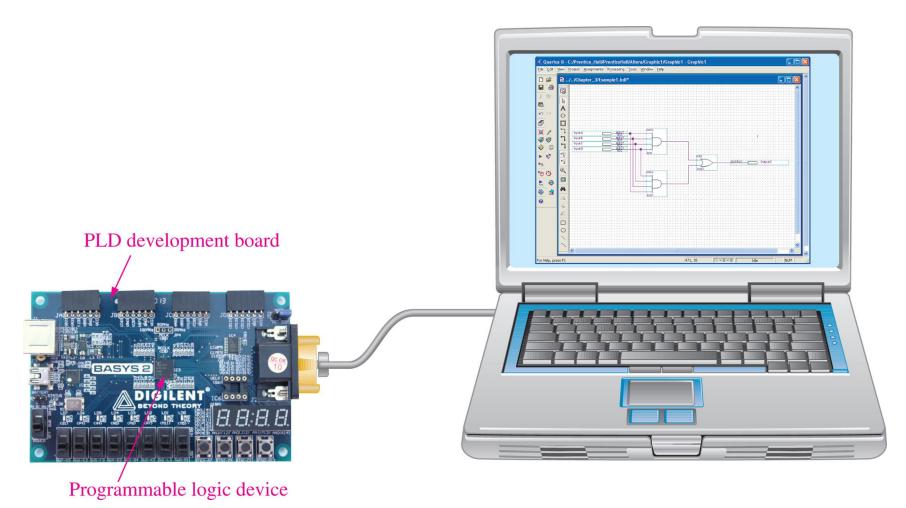

**FIGURE 3-55** Programming setup for reprogrammable logic devices. (Photo courtesy of Digilent, Inc.)

3 – Logic Gates

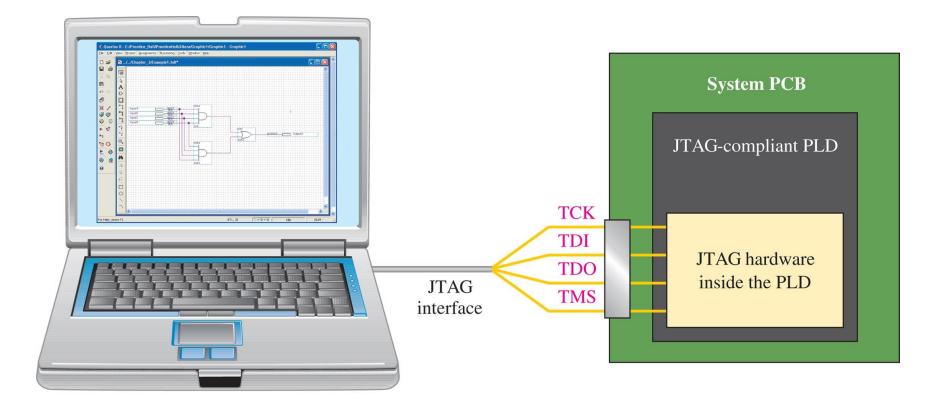

**FIGURE 3-57** Simplified illustration of in-system programming via a JTAG interface.

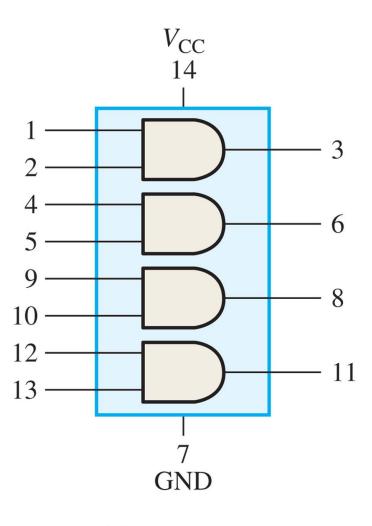

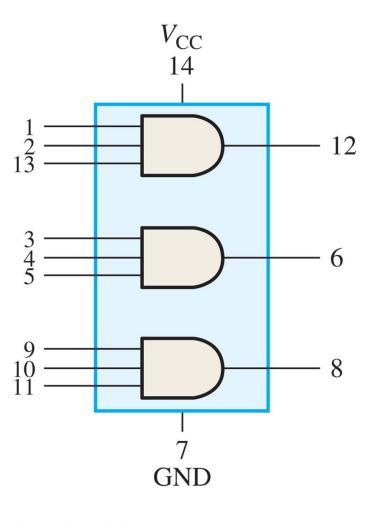

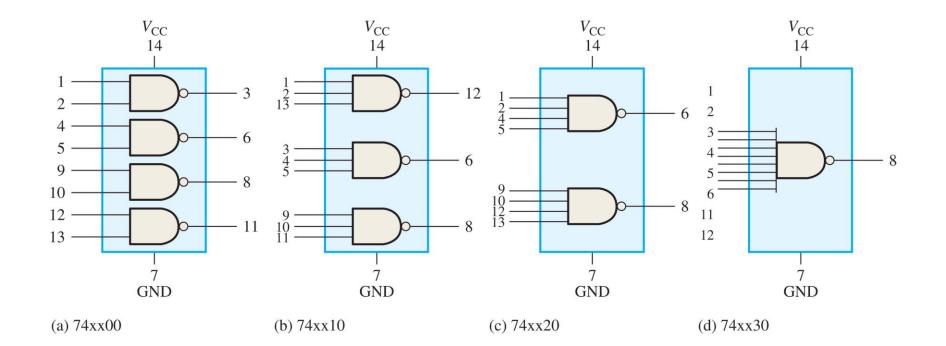

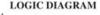

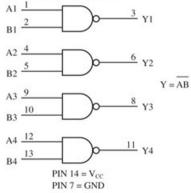

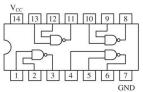

**FIGURE 3-59** 74 series AND gate devices with pin numbers.

(a) 74xx08

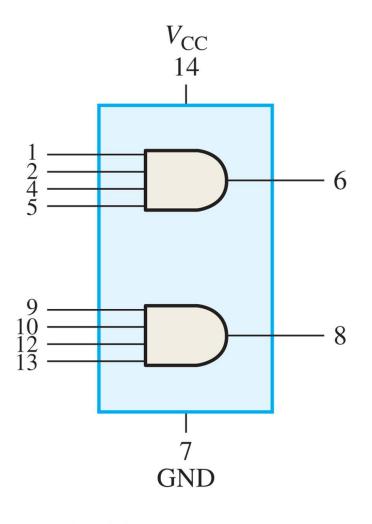

**FIGURE 3-59 (continued)** 74 series AND gate devices with pin numbers.

(b) 74xx11

**FIGURE 3-59 (continued)** 74 series AND gate devices with pin numbers.

(c) 74xx21

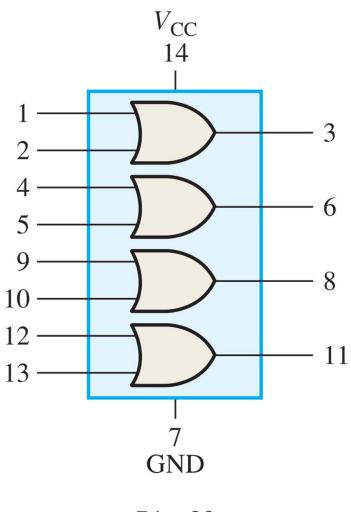

**FIGURE 3-61** 74 series OR gate device.

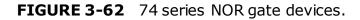

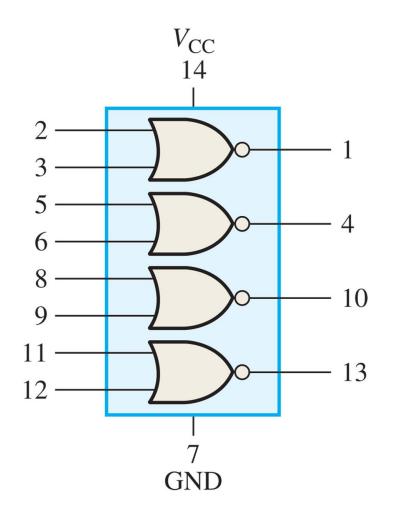

(a) 74xx02

(b) 74xx27

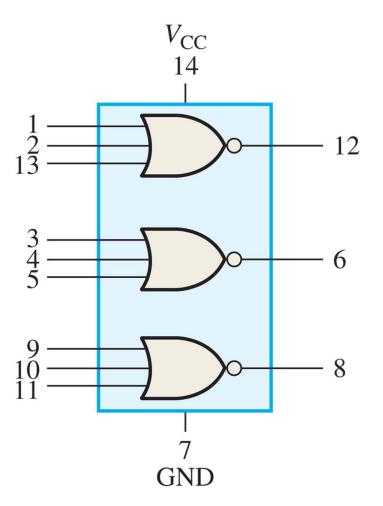

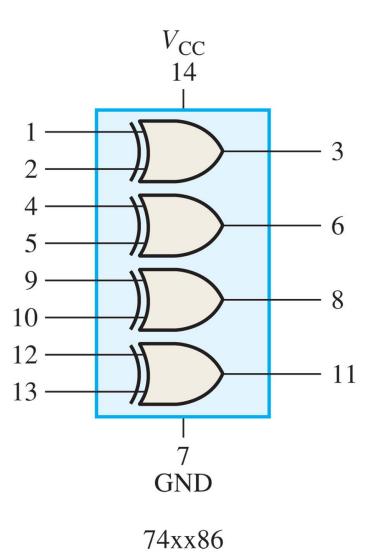

# FIGURE 3-63 74 series XOR gate.

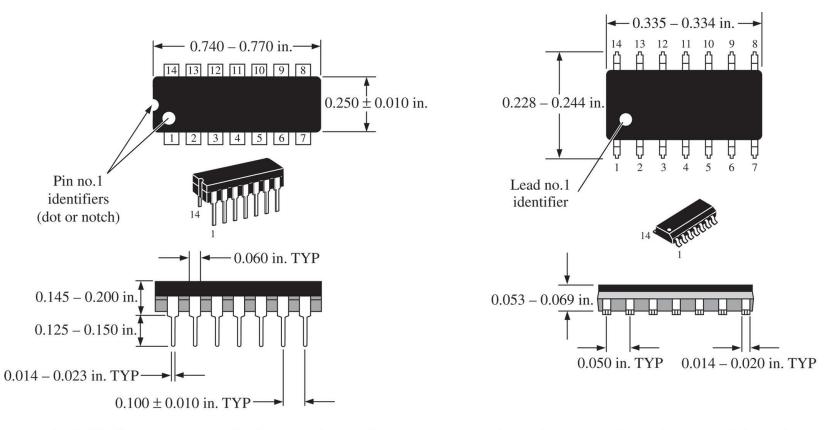

**FIGURE 3-64** Typical dual in-line (DIP) and small-outline (SOIC) packages showing pin numbers and basic dimensions.

(a) 14-pin dual in-line package (DIP) for feedthrough mounting

(b) 14-pin small outline package (SOIC) for surface mounting

# **TABLE 3–14**

# 74 series logic families based on circuit technology.

| Circuit Type | Description                     | Circuit Technology |

|--------------|---------------------------------|--------------------|

| ABT          | Advanced BiCMOS                 | BiCMOS             |

| AC           | Advanced CMOS                   | CMOS               |

| ACT          | Bipolar compatible AC           | CMOS               |

| AHC          | Advanced high-speed CMOS        | CMOS               |

| AHCT         | Bipolar compatible AHC          | CMOS               |

| ALB          | Advanced low-voltage BiCMOS     | BiCMOS             |

| ALS          | Advanced low-power Schottky     | Bipolar            |

| ALVC         | Advanced low-voltage CMOS       | CMOS               |

| AUC          | Advanced ultra-low-voltage CMOS | CMOS               |

| AUP          | Advanced ultra-low-power CMOS   | CMOS               |

| AS           | Advanced Schottky               | Bipolar            |

| AVC          | Advanced very-low-power CMOS    | CMOS               |

| BCT          | Standard BiCMOS                 | BiCMOS             |

| F            | Fast                            | Bipolar            |

| FCT          | Fast CMOS technology            | CMOS               |

| HC           | High-speed CMOS                 | CMOS               |

| HCT          | Bipolar compatible HC           | CMOS               |

| LS           | Low-power Schottky              | Bipolar            |

| LV-A         | Low-voltage CMOS                | CMOS               |

| LV-AT        | Bipolar compatible LV-A         | CMOS               |

| LVC          | Low-voltage CMOS                | CMOS               |

| LVT          | Low-voltage biCMOS              | BiCMOS             |

| S            | Schottky                        | Bipolar            |

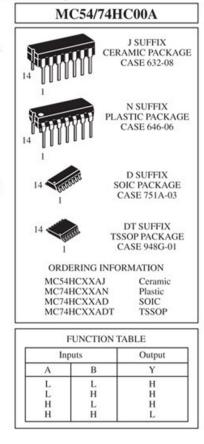

# **FIGURE 3-65** CMOS logic. Partial data sheet for a 54/74HC00A quad 2-input NAND gate. The 54 prefix indicates military grade and the 74 prefix indicates commercial grade.

### Quad 2-Input NAND Gate High-Performance Silicon-Gate CMOS

The MC54/74HC00A is identical in pinout to the LS00. The device inputs are compatible with Standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.

- · Output Drive Capability: 10 LSTTL Loads

- · Outputs Directly Interface to CMOS, NMOS and TTL

- Operating Voltage Range: 2 to 6 V

- Low Input Current: 1 μA

- High Noise Immunity Characteristic of CMOS Devices

- In Compliance With the JEDEC Standard No. 7A Requirements

- Chip Complexity: 32 FETs or 8 Equivalent Gates

Pinout: 14-Load Packages (Top View)

#### MAXIMUM RATINGS\*

| Symbol           | Parameter                                                                             | Value                         | Unit |

|------------------|---------------------------------------------------------------------------------------|-------------------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage (Referenced to GND)                                                 | -0.5 to + 7.0                 | V    |

| Vin              | DC Input Voltage (Referenced to GND)                                                  | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| Vout             | DC Output Voltage (Referenced to GND)                                                 | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| Iin              | DC Input Current, per Pin                                                             | ± 20                          | mA   |

| Iout             | DC Output Current, per Pin                                                            | ± 25                          | mA   |

| Icc              | DC Supply Current, V <sub>CC</sub> and GND Pins                                       | ± 50                          | mA   |

| PD               | Power Dissipation in Still Air, Plastic or Ceramic DIP+                               | 750                           | mW   |

|                  | SOIC Package†                                                                         | 500                           |      |

|                  | TSSOP Package+                                                                        | 450                           |      |

| T <sub>stg</sub> | Storage Temperature                                                                   | -65 to + 150                  | °C   |

| TL               | Lead Temperature, 1 mm from Case for 10 Seconds<br>Plastic DIP, SOIC or TSSOP Package | 260                           | °C   |

|                  | Ceramic DIP                                                                           | 300                           |      |

\* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

† Derating — Plastic DIP: - 10 mW/°C from 65° to 125° C Ceramic DIP: - 10 mW/°C from 100° to 125° C SOIC Package: - 7 mW/°C from 65° to 125° C TSSOP Package: - 6.1 mW/°C from 65° to 125° C

#### RECOMMENDED OPERATING CONDITIONS

| Symbol                          | Parameter                                            |            | in   | Max     | Unit |  |

|---------------------------------|------------------------------------------------------|------------|------|---------|------|--|

| V <sub>CC</sub>                 | DC Supply Voltage (Referenced to GND)                |            | 2.0  | 2.0 6.0 |      |  |

| Vin, Vout                       | DC Input Voltage, Output Voltage (Referenced to GND) |            | 0    | Vcc     | V    |  |

| TA                              | Operating Temperature, All Package Types             | -55        | +125 | °C      |      |  |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise and Fall Time V                           | cc = 2.0 V | 0    | 1000    | ns   |  |

|                                 | v                                                    | cc = 4.5 V | 0    | 500     | 1.00 |  |

|                                 | v                                                    | cc = 6.0 V | 0    | 400     |      |  |

**FIGURE 3-65 (continued)** CMOS logic. Partial data sheet for a 54/74HC00A quad 2-input NAND gate. The 54 prefix indicates military grade and the 74 prefix indicates commercial grade.

|                                       |                                                   |                                                                     | Vcc   | Guaranteed Limit |              |      |      |  |

|---------------------------------------|---------------------------------------------------|---------------------------------------------------------------------|-------|------------------|--------------|------|------|--|

| Symbol                                | Parameter                                         | Condition                                                           | V     | -55 to 25°C      | ≤85°C ≤125°C |      | Unit |  |

| VIH                                   | Minimum High-Level Input Voltage                  | $V_{out} = 0.1 V \text{ or } V_{CC} - 0.1 V$                        | 2.0   | 1.50             | 1.50         | 1.50 | V    |  |

|                                       |                                                   | $ I_{out}  \le 20\mu A$                                             | 3.0   | 2.10             | 2.10         | 2.10 |      |  |

|                                       |                                                   |                                                                     | 4.5   | 3.15             | 3.15         | 3.15 |      |  |

|                                       |                                                   |                                                                     | 6.0   | 4.20             | 4.20         | 4.20 |      |  |

| VIL                                   | Maximum Low-Level Input Voltage                   | $V_{out} = 0.1 V \text{ or } V_{CC} - 0.1 V$                        | 2.0   | 0.50             | 0.50         | 0.50 | V    |  |

|                                       |                                                   | $ I_{out}  \le 20\mu A$                                             | 3.0   | 0.90             | 0.90         | 0.90 |      |  |

|                                       |                                                   |                                                                     | 4.5   | 1.35             | 1.35         | 1.35 |      |  |

|                                       |                                                   |                                                                     | 6.0   | 1.80             | 1.80         | 1.80 |      |  |

| VOH Minimum High-Level Output Voltage | $V_{in} = V_{IH}$ or $V_{IL}$                     | 2.0                                                                 | 1.9   | 1.9              | 1.9          | V    |      |  |

|                                       |                                                   | $ I_{out}  \le 20 \mu A$                                            | 4.5   | 4.4              | 4.4          | 4.4  |      |  |

|                                       |                                                   |                                                                     | 6.0   | 5.9              | 5.9          | 5.9  |      |  |

|                                       |                                                   | $V_{in} = V_{IH}$ or $V_{IL}$ $ I_{out}  \le 2.4 \text{m}$ .        | A 3.0 | 2.48             | 2.34         | 2.20 |      |  |

|                                       |                                                   | I <sub>out</sub>   ≤4.0m                                            | A 4.5 | 3.98             | 3.84         | 3.70 |      |  |

|                                       |                                                   | I <sub>out</sub>   ≤5.2m                                            | A 6.0 | 5.48             | 5.34         | 5.20 |      |  |

| VOL                                   | Maximum Low-Level Output Voltage                  | $V_{in} = V_{IH}$ or $V_{IL}$                                       | 2.0   | 0.1              | 0.1          | 0.1  | V    |  |

|                                       |                                                   | $ I_{out}  \le 20 \mu A$                                            | 4.5   | 0.1              | 0.1          | 0.1  |      |  |

|                                       |                                                   |                                                                     | 6.0   | 0.1              | 0.1          | 0.1  |      |  |

|                                       |                                                   | $V_{in} = V_{IH} \text{ or } V_{IL}$ $ I_{out}  \le 2.4 \text{ m}.$ | A 3.0 | 0.26             | 0.33         | 0.40 | 1    |  |

|                                       |                                                   | I <sub>out</sub>   ≤4.0m.                                           |       | 0.26             | 0.33         | 0.40 |      |  |

|                                       |                                                   | I <sub>out</sub>   ≤ 5.2m.                                          |       | 0.26             | 0.33         | 0.40 | I .  |  |

| Iin                                   | Maximum Input Leakage Current                     | V <sub>in</sub> = V <sub>CC</sub> or GND                            | 6.0   | ±0.1             | ±1.0         | ±1.0 | μA   |  |

| I <sub>CC</sub>                       | Maximum Quiescent Supply<br>Current (per Package) | $V_{in} = V_{CC}$ or GND<br>$I_{out} = 0\mu A$                      | 6.0   | 1.0              | 10           | 40   | μA   |  |

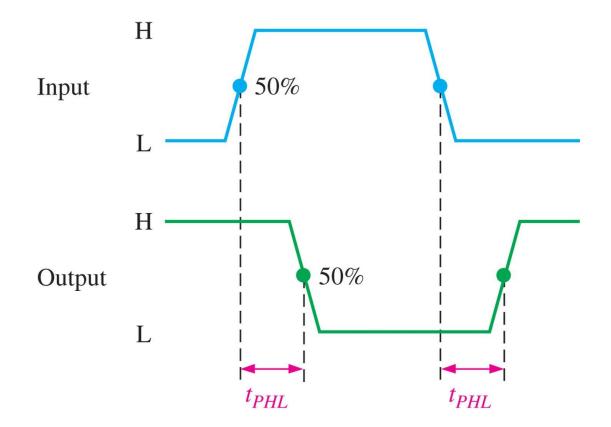

#### AC CHARACTERISTICS ( $C_L = 50 \text{ pF}$ , Input $t_r = t_f = 6 \text{ ns}$ )

|                    |                                                                                                       | Vcc | Gu          | aranteed Li | nit                         |      |

|--------------------|-------------------------------------------------------------------------------------------------------|-----|-------------|-------------|-----------------------------|------|

| Symbol             | Parameter                                                                                             | V   | -55 to 25°C | ≤85°C       | ≤125°C                      | Unit |

| tpLH.              | Maximum Propagation Delay, Input A or B to Output Y                                                   | 2.0 | 75          | 95          | 110                         | ns   |

| <b>t</b> PHL       | 에는 가지 않는 사람이 있는 것은 것이 있는 것은 것이 있다. 그 것은 것은 것 같은 것은 것 같은 것은 것 같은 것은 것 같이 있다. 것 같이 있는 것 같이 있다. 것 같이 있다. | 3.0 | 30          | 40          | 55                          |      |

|                    |                                                                                                       | 4.5 | 15          | 19          | 22                          | 1    |

|                    |                                                                                                       | 6.0 | 13          | 16          | 19                          |      |

| t <sub>TLH</sub> , | Maximum Output Transition Time, Any Output                                                            | 2.0 | 75          | 95          | 110                         | ns   |

| t <sub>THL</sub>   |                                                                                                       | 3.0 | 27          | 32          | 36                          |      |

|                    |                                                                                                       | 4.5 | 15          | 19          | 22                          | 1    |

|                    |                                                                                                       | 6.0 | 13          | 16          | 55<br>22<br>19<br>110<br>36 |      |

| Cin                | Maximum Input Capacitance                                                                             |     | 10          | 10          | 10                          | pF   |

|     |                                            | Typical @ $25^{\circ}$ C, V <sub>CC</sub> = 5.0 V, V <sub>EE</sub> = 0 V |    |

|-----|--------------------------------------------|--------------------------------------------------------------------------|----|

| CPD | Power Dissipation Capacitance (Per Buffer) | 22                                                                       | pF |

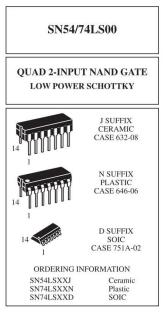

### **FIGURE 3-66** Bipolar logic. Partial data sheet for a 54/74LS00 quad 2-input NAND gate.

#### **QUAD 2-INPUT NAND GATE**

• ESD > 3500 Volts

|                 |                                            |        |             | Limits |      | Limits          |                                                                     |   |                                                 |  |  |

|-----------------|--------------------------------------------|--------|-------------|--------|------|-----------------|---------------------------------------------------------------------|---|-------------------------------------------------|--|--|

| Symbol          | Parameter                                  |        | Min Typ Max |        | Unit | Test Conditions |                                                                     |   |                                                 |  |  |

| V <sub>IH</sub> | Input HIGH Voltage                         |        | 2.0         | 2.0    |      |                 |                                                                     | V | Guaranteed Input HIGH Voltage for<br>All Inputs |  |  |

| VIL             | Input LOW Voltage                          | 54     |             |        | 0.7  | v               | Guaranteed Input LOW Voltage for                                    |   |                                                 |  |  |

| * IL            | input LOW Voltage                          | 74     |             |        | 0.8  | ľ               | All Inputs                                                          |   |                                                 |  |  |

| V <sub>IK</sub> | Input Clamp Diode Voltage                  |        |             | -0.65  | -1.5 | V               | $V_{CC} = MIN, I_{IN} = -18 \text{ mA}$                             |   |                                                 |  |  |

| V <sub>OH</sub> | Ouput HIGH Voltage                         | 54     | 2.5         | 3.5    |      | V               | $V_{CC} = MIN, I_{OH} = MAX, V_{IN} = V_{IH}$                       |   |                                                 |  |  |

| * OH            | Ouput HIGH voltage                         | 74     | 2.7         | 3.5    |      | v               | or V <sub>IL</sub> per Truth Table                                  |   |                                                 |  |  |

| VOL             | Ouput LOW Voltage                          | 54, 74 |             | 0.25   | 0.4  | V               | $I_{OL} = 4.0 \text{ mA}$ $V_{CC} = V_{CC} \text{ MIN}, V_{IN} = V$ |   |                                                 |  |  |

| * OL            | ouput Dow voltage                          | 74     |             | 0.35   | 0.5  | V               | $I_{OL} = 8.0 \text{ mA}$ or $V_{IH}$ per Truth Table               |   |                                                 |  |  |

| I <sub>IH</sub> | Input HIGH Current                         |        |             |        | 20   | μΑ              | $V_{CC} = MAX, V_{IN} = 2.7 V$                                      |   |                                                 |  |  |

| ЧH              | mput mon cuntur                            |        |             |        | 0.1  | mA              | $V_{CC} = MAX, V_{IN} = 7.0 V$                                      |   |                                                 |  |  |

| I <sub>IL</sub> | Input LOW Current                          |        |             |        | -0.4 | mA              | $V_{CC} = MAX, I_N = 0.4 V$                                         |   |                                                 |  |  |

| I <sub>OS</sub> | Short Circuit Current (Note 1              | )      | -20         |        | -100 | mA              | $V_{CC} = MAX$                                                      |   |                                                 |  |  |

| I <sub>CC</sub> | Power Supply Current<br>Total, Output HIGH |        |             |        | 1.6  | mA              | V <sub>CC</sub> = MAX                                               |   |                                                 |  |  |

|                 | Total, Output LOW                          |        |             | 4.4    | 1    | 0.02            |                                                                     |   |                                                 |  |  |

NOTE 1: Not more than one output should be shorted at a time, nor for more than 1 second.

#### AC CHARACTERISTICS ( $T_A = 25^{\circ}C$ )

|                  |                                 |     | Limits |     |      |                       |

|------------------|---------------------------------|-----|--------|-----|------|-----------------------|

| Symbol           | Parameter                       | Min | Тур    | Max | Unit | Test Conditions       |

| t <sub>PLH</sub> | Turn-Off Delay, Input to Output |     | 9.0    | 15  | ns   | $V_{CC} = 5.0 V$      |

| t <sub>PHL</sub> | Turn-On Delay, Input to Output  |     | 10     | 15  | ns   | $C_L = 15 \text{ pF}$ |

#### GUARANTEED OPERATING RANGES

| Symbol          | Parameter             |        | Min  | Тур | Max  | Unit |

|-----------------|-----------------------|--------|------|-----|------|------|

| V <sub>CC</sub> | Supply Voltage        | 54     | 4.5  | 5.0 | 5.5  | V    |

|                 |                       | 74     | 4.75 | 5.0 | 5.25 |      |

| T <sub>A</sub>  | Operating Ambient     | 54     | -55  | 25  | 125  | °C   |

|                 | Temperature Range     | 74     | 0    | 25  | 70   |      |

| I <sub>OH</sub> | Output Current — High | 54, 74 |      |     | -0.4 | mA   |

| IOL             | Output Current — Low  | 54     |      |     | 4.0  | mA   |

|                 |                       | 74     |      |     | 8.0  |      |

#### SN54/74LS00

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

## **FIGURE 3-67**

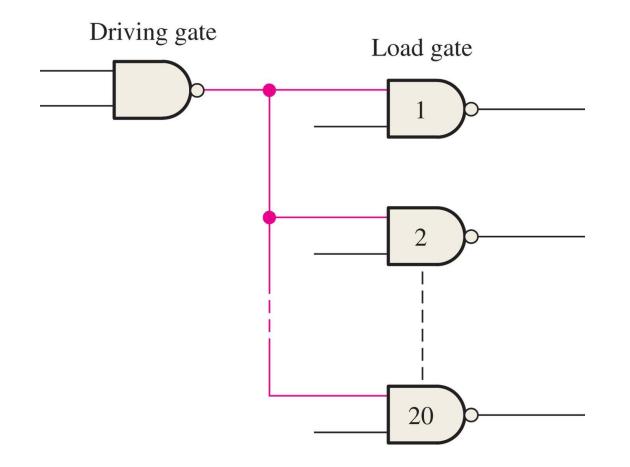

**FIGURE 3-68** The LS family NAND gate output fans out to a maximum of 20 LS family gate inputs.

Electronics II

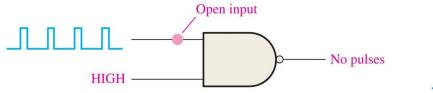

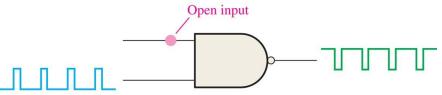

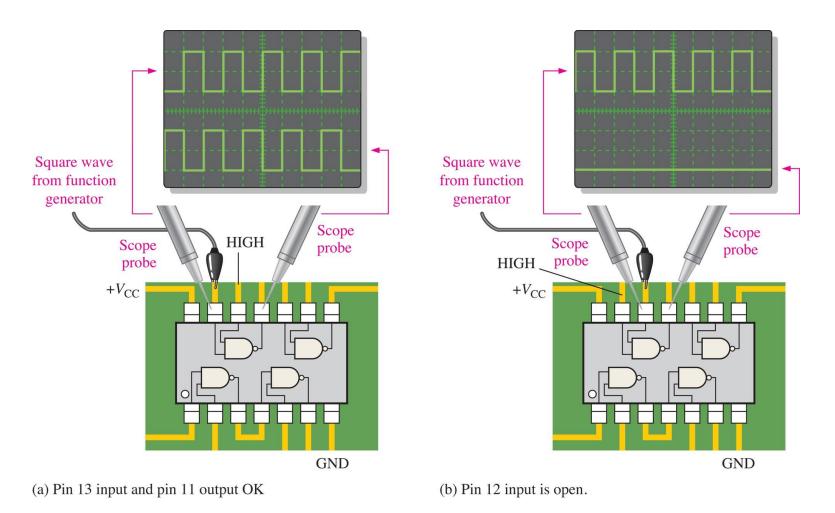

**FIGURE 3-69** The effect of an open input on a NAND gate.

- (a) Application of pulses to the open input will produce no pulses on the output.

- (b) Application of pulses to the good input will produce output pulses for bipolar NAND and AND gates because an open input typically acts as a HIGH. It is uncertain for CMOS.

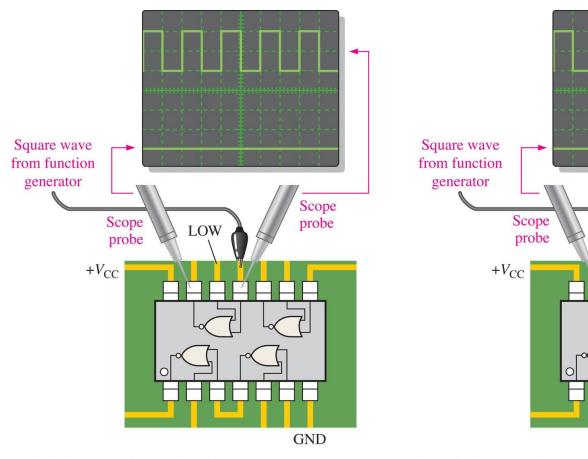

# **FIGURE 3-71** Troubleshooting a NOR gate for an open output.

(a) Pulse input on pin 11. No pulse output.

(b) Pulse input on pin 12. No pulse output.

Scope

probe

LOW

GND

### **FIGURE 3-73**

(a) The counter is working properly.

## FIGURE 3-73 (continued)

(b) The counter is not measuring a frequency.